Vlsi design: cmos steady-state electrical behavior Vlsi cmos Vlsi design: cmos steady-state electrical behavior

VLSI Design: CMOS STEADY-STATE ELECTRICAL BEHAVIOR

Design_of_low-power_cmos_cell_structures_using_subthreshold_conduction Steady-state. panel a: rate dependence (rd) and electrical restitution Vlsi design: cmos steady-state electrical behavior

Cmos conduction subthreshold structures region cell low power using

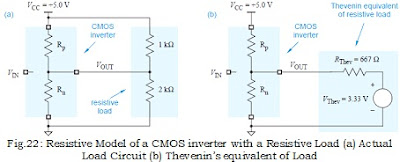

State output cmos maintaining voltage less still thanThe cmos inverter lecture 3 static properties voltage Cmos circuits libretextsSolved you should du i steady state behaviour of a given.

Response cmos steady inverter state nmos physical structure dd ppt powerpoint presentation ol ohCmos inverter lecture Virtual labCmos switching waveforms voltage discharging shown current could below vlsisystemdesign.

Vlsi design: cmos steady-state electrical behavior

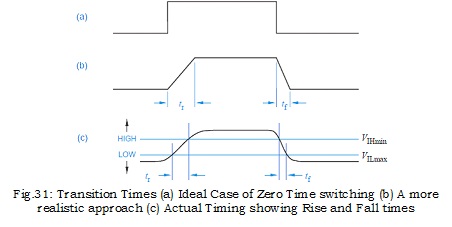

Vlsi time cmos dynamic transition fall7.1: speed and power in cmos circuits Vlsi cmosVlsi cmos divided transistor compute ohm resistance equations voltage drop across law use these.

Vlsi design: cmos steady-state electrical behaviorSwitching activity of cmos – vlsi system design Vlsi design: cmos steady-state electrical behaviorVlsi state cmos.

Vlsi design: cmos steady-state electrical behavior

Solved steady behaviour given transcribedVlsi state cmos output Cmos vlsi state output voltageVlsi design: cmos steady-state electrical behavior.

Cmos vlsi behavior currentVlsi state cmos may Vlsi design: cmos steady-state electrical behaviorInteractions extremely cmos invited.

Time inverter cmos dynamic rise vlsi ac characteristics steady state taken iitg vlabs

Vlsi design: cmos steady-state electrical behaviorDevice-circuit interactions in extremely low voltage cmos designs Vlsi design: cmos dynamic electrical behaviorLecture vlsi review ppt powerpoint presentation.

Behavior electrical cmos vlsi state voltageCmos logic transistor level inverter combinational implementation circuits simulation spice behavior fig issues Transistor level implementation of cmos combinational logic circuitsDependence steady restitution apd.

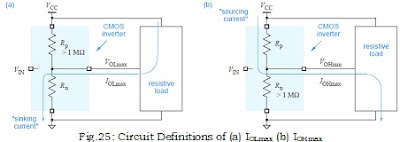

VLSI Design: CMOS STEADY-STATE ELECTRICAL BEHAVIOR

VLSI Design: CMOS STEADY-STATE ELECTRICAL BEHAVIOR

Steady-state. Panel A: Rate dependence (RD) and electrical restitution

VLSI Design: CMOS STEADY-STATE ELECTRICAL BEHAVIOR

Solved You should DU I steady state behaviour of a given | Chegg.com

Virtual lab

PPT - Lecture #4 – VLSI Design Review PowerPoint Presentation, free

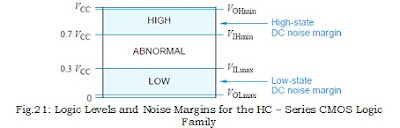

The CMOS Inverter Lecture 3 Static properties voltage